Arquitetura de Computadores

1. Operações Fundamentais de um Computador

• Entra da (Input): Recebe dados do usuário ou de dispositivos externos.

• Componen te responsável : Dispositivos de entrada (t eclado, mouse).

• Processamento : Executa operações l ógicas e aritméticas.

Compon ente responsável: CPU (Unidade Lógica e Aritmética – ULA).

• Saída (Output): Exibe ou envia resultados.

Compon ente responsável: Dispositivos de saída (monitor, impressora).

• Arma zenamento: Guarda dados temporária ou permanent emente.

Compon ente responsável: Memória RAM (volátil) ou HD/SSD (não volátil).

2. Funções da UCP (Unidade Central de

Processamento)

A CPU tem duas funções principais:

1. Busca (Fetch): Acessa a memó ria para obter instruções (gerenciado pela

Unida de de Controle).

2. Exe cução (Execute): Processa a s instruções usando a ULA.

Relação com componentes interno s:

• Unidade de Controle → Coordena o fl uxo de dados.

• ULA → Realiza cálculos e operações lógicas.

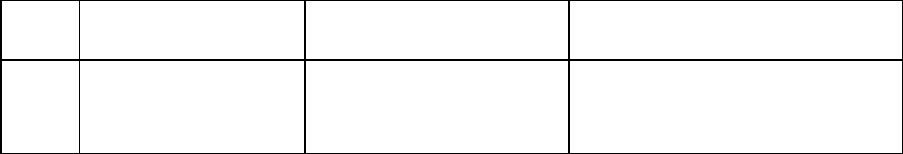

3. Barramentos

Tipo

Direcionalidade

Função

Exem plo

Dad

os

Bidi recional

Transpo rta dados

entre CPU e memória

Transf erência de um arquivo

da RAM pa ra a CPU

End

ereç

os

Uni direcional (CPU

→ memória)

In dica posições de

memória

CPU l ê o dado arma zena do

no endereço 0xA1B2

Cont

role

Bidi recional

Gerencia operaçõ es

(leit ura/escrita )

Sinal de clock, reset,

handsha ke

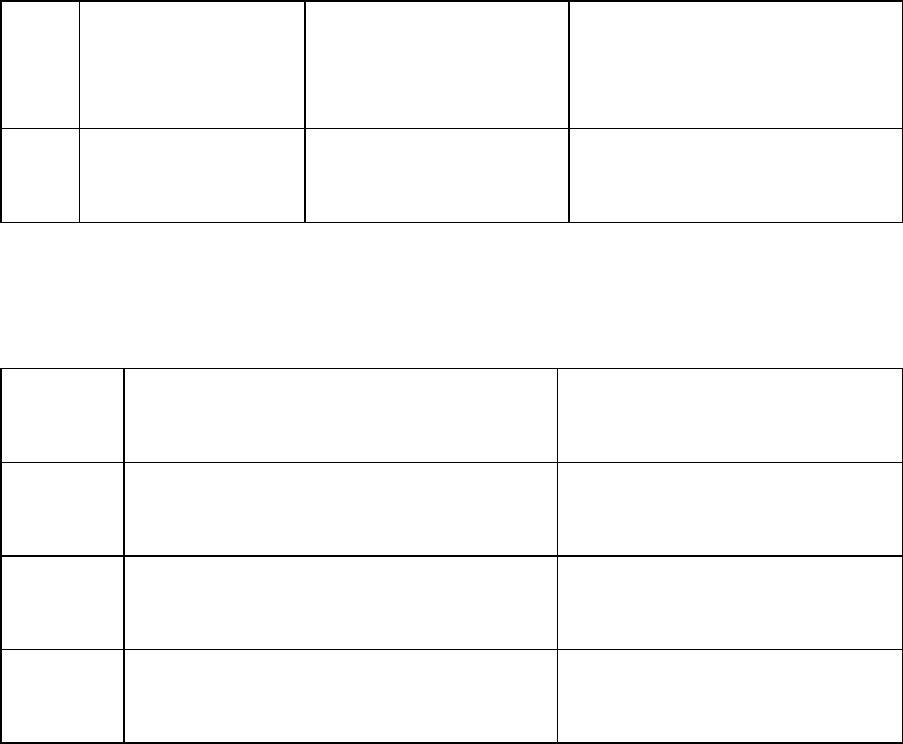

4. CISC vs RISC

Cara cter

ística

CISC (ex.: Intel x86)

RISC (ex.: ARM, MIPS)

Complex

idade

In struções compl exas (1 comando =

múltiplas o perações)

In struções simpl es (1

comando = 1 operação)

Vantage

ns

Código mais compa cto

Efi ciência energética e

paraleli smo

Desvant

age ns

Consumo elevado de energia

Mai s in struções para tarefa s

complexas

5. Lei de Moore

• Definição: A quantidade de transistores em um chip dobra a cada ~2 anos,

aumentando o desempenho.

• Valida de atual: Ainda se aplica, ma s enf renta desaf ios físicos (limites de

miniaturi zação, aquecimento).

• Desafios:

o Leakage de energia em t ransistores nanométri cos.

o Alto s custos de fabri cação em processos abaixo de 5nm.

6. Hierarquia de Memória

Ordem (do mais rápido ao mais lento):

1. Registra dores (dentro da CPU, acesso i mediato).

2. Cache L1/L2/L3 (vel ocidade int ermediária, armazena dados frequentes).

3. Memória RAM (v olátil, armazenamento principal).

4. Arma zenamento secundário (SSD/HD, não volátil, grande capacidade).

Objetivo: Equilibra r velocidade, custo e capacidade.

7. Modelo de Von Neumann

• Compo nentes principais:

o CPU (processamento).

o Memória (armazena dados e instruções).

o Dispositivos de E/S (entrada e saí da).

o Barram entos (comunicação entre componen tes).

• Relevância atual: P ermite flexibilidade (programas armazenados em memória).

8. Pipeline e Paralelismo

• Pipeline: Divide a execução de instruções em estágios (ex.: fetch, decode,

execute) pa ra sobrepo sição.

Impacto : Aumenta vazão, mas pode causar hazards (conflito s).

• Para lelismo (Superescalar): Executa múltiplas instruções simultaneamente

(usando vá rias ULAs).

Impacto : Melhor desempenho, mas maior complexidade.

9. Gerações de Computadores

• 3ª Geração (1965 –1975):

o Tecnolo gia: Circuitos integrados (transistores em chips).

o Exemplo: IBM System/360.

• 4ª Geração (1975 –1990):

o Tecnolo gia: Microprocessadores (CPU em um único ch ip).

o Exemplo: PCs com Intel 8086.

10 . Memória Cache

• Função : Reduzir o tempo de acesso à memória princi pal (RAM).

• Níveis:

o L1: Mais rápido (1-2 ciclos de CPU), menor (KB), dentro do núcleo.

o L2: Intermediário (MB), pode ser compartilhado entre núcleos.

o L3: Mais lento (MB/GB), compartilha do por toda a CPU.

Observação: Este documento está formatado para ser copiado diretamente para o

Microsoft Word. Pa ra melhor visualização, utilize:

• Font e Arial ou Times New Roman 12 .

• Títulos em negrito.

• Tabela s com bo rdas visív eis.

Prévia do material em texto

Arquitetura de Computadores 1. Operações Fundamentais de um Computador • Entrada (Input): Recebe dados do usuário ou de dispositivos externos. • Componente responsável: Dispositivos de entrada (teclado, mouse). • Processamento: Executa operações lógicas e aritméticas. Componente responsável: CPU (Unidade Lógica e Aritmética – ULA). • Saída (Output): Exibe ou envia resultados. Componente responsável: Dispositivos de saída (monitor, impressora). • Armazenamento: Guarda dados temporária ou permanentemente. Componente responsável: Memória RAM (volátil) ou HD/SSD (não volátil). 2. Funções da UCP (Unidade Central de Processamento) A CPU tem duas funções principais: 1. Busca (Fetch): Acessa a memória para obter instruções (gerenciado pela Unidade de Controle). 2. Execução (Execute): Processa as instruções usando a ULA. Relação com componentes internos: • Unidade de Controle → Coordena o fluxo de dados. • ULA → Realiza cálculos e operações lógicas. 3. Barramentos Tipo Direcionalidade Função Exemplo Dad os Bidirecional Transporta dados entre CPU e memória Transferência de um arquivo da RAM para a CPU End ereç os Unidirecional (CPU → memória) Indica posições de memória CPU lê o dado armazenado no endereço 0xA1B2 Cont role Bidirecional Gerencia operações (leitura/escrita) Sinal de clock, reset, handshake 4. CISC vs RISC Caracter ística CISC (ex.: Intel x86) RISC (ex.: ARM, MIPS) Complex idade Instruções complexas (1 comando = múltiplas operações) Instruções simples (1 comando = 1 operação) Vantage ns Código mais compacto Eficiência energética e paralelismo Desvant agens Consumo elevado de energia Mais instruções para tarefas complexas 5. Lei de Moore • Definição: A quantidade de transistores em um chip dobra a cada ~2 anos, aumentando o desempenho. • Validade atual: Ainda se aplica, mas enfrenta desafios físicos (limites de miniaturização, aquecimento). • Desafios: o Leakage de energia em transistores nanométricos. o Altos custos de fabricação em processos abaixo de 5nm. 6. Hierarquia de Memória Ordem (do mais rápido ao mais lento): 1. Registradores (dentro da CPU, acesso imediato). 2. Cache L1/L2/L3 (velocidade intermediária, armazena dados frequentes). 3. Memória RAM (volátil, armazenamento principal). 4. Armazenamento secundário (SSD/HD, não volátil, grande capacidade). Objetivo: Equilibrar velocidade, custo e capacidade. 7. Modelo de Von Neumann • Componentes principais: o CPU (processamento). o Memória (armazena dados e instruções). o Dispositivos de E/S (entrada e saída). o Barramentos (comunicação entre componentes). • Relevância atual: Permite flexibilidade (programas armazenados em memória). 8. Pipeline e Paralelismo • Pipeline: Divide a execução de instruções em estágios (ex.: fetch, decode, execute) para sobreposição. Impacto: Aumenta vazão, mas pode causar hazards (conflitos). • Paralelismo (Superescalar): Executa múltiplas instruções simultaneamente (usando várias ULAs). Impacto: Melhor desempenho, mas maior complexidade. 9. Gerações de Computadores • 3ª Geração (1965–1975): o Tecnologia: Circuitos integrados (transistores em chips). o Exemplo: IBM System/360. • 4ª Geração (1975–1990): o Tecnologia: Microprocessadores (CPU em um único chip). o Exemplo: PCs com Intel 8086. 10. Memória Cache • Função: Reduzir o tempo de acesso à memória principal (RAM). • Níveis: o L1: Mais rápido (1-2 ciclos de CPU), menor (KB), dentro do núcleo. o L2: Intermediário (MB), pode ser compartilhado entre núcleos. o L3: Mais lento (MB/GB), compartilhado por toda a CPU. Observação: Este documento está formatado para ser copiado diretamente para o Microsoft Word. Para melhor visualização, utilize: • Fonte Arial ou Times New Roman 12. • Títulos em negrito. • Tabelas com bordas visíveis. Arquitetura de Computadores 1. Operações Fundamentais de um Computador 2. Funções da UCP (Unidade Central de Processamento) 3. Barramentos 4. CISC vs RISC 5. Lei de Moore 6. Hierarquia de Memória 7. Modelo de Von Neumann 8. Pipeline e Paralelismo 9. Gerações de Computadores 10. Memória Cache